ELSEVIER

Contents lists available at ScienceDirect

### Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

## Investigation of scalability of In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well field effect transistor (QWFET) architecture for logic applications

E. Hwang a,\*, S. Mookerjea a, M.K. Hudait b, S. Datta a

#### ARTICLE INFO

# Article history: Received 7 October 2010 Received in revised form 7 April 2011 Accepted 12 April 2011 Available online 4 May 2011

The review of this paper was arranged by Prof. S. Cristoloveanu

Keywords: InGaAs Quantum well FETs (QWFETs) Drift-Diffusion simulation Ballistic effect Effective carrier injection velocity Double-Gate (DG) QWFETs

#### ABSTRACT

In this paper, the scalability of  $In_{0.7}Ga_{0.3}As$  QWFET is investigated using two-dimensional numerical drift-diffusion simulation. Numerical drift-diffusion simulations were calibrated using experimental results on short-channel  $In_{0.7}Ga_{0.3}As$  QWFETs [7] to include the effects of velocity overshoot. Logic figures of merit (sub-threshold slope, saturated threshold voltage, drain induced barrier lowering,  $I_{0N}/I_{OFF}$  ratio over a specified gate swing, effective injection velocity and intrinsic switching delay) extracted from the numerical simulations are in excellent agreement with the experimental data. Three alternate QWFET device architectures are proposed and thoroughly investigated for 15 nm node and beyond logic applications. Amongst them, double-gate  $In_{0.7}Ga_{0.3}As$  QWFET shows the best scalability in terms of logic figures of merit, thus making it an ideal candidate for the design and demonstration of the ultimate scaled transistor.

© 2011 Elsevier Ltd. All rights reserved.

#### 1. Introduction

In today's multi-core CPU era, as the dimension of silicon CMOS continues to scale to meet the ever increasing demand for higher transistor count, the rising power dissipation (both static and dynamic) has been identified as the critical brick wall to transistor scaling [1]. Aggressive supply voltage scaling to 0.5 V and below while maintaining transistor performance is a direct path toward reducing power consumption. In this regard, III-V compound semiconductor based quantum well field effect transistors (QWFETs) have recently attracted attention for low-power logic applications [2–4]. High indium content indium gallium arsenide (In<sub>0.7</sub>Ga<sub>0.3</sub>As). indium arsenide (InAs) and indium antimonide (InSb) QWFETs exhibit excellent electron transport property at both low and high electric fields arising from a combination of: (i) low  $\Gamma$ -valley electron mass, (ii) reduced impurity scattering due to modulation doping, (iii) reduced interface roughness scattering because of epitaxially grown smooth interfaces and (iv) large energetic separation between  $\Gamma$  and L-valleys. The low electron transport mass coupled with minimal back scattering from the channel back into the source gives rise to higher source side effective injection carrier velocity ( $v_{\rm eff}$ ). The expected enhancement in injection velocity is

sufficient to compensate for lower carrier density in the channel of III–V QWFETs due to the reduced density of states from lower band mass compared to Si MOSFETs, and, hence, expected to deliver higher ON-current particularly at reduced supply voltages compared to Si MOSFETs, thus enabling supply voltage scaling [5,6]. However, a key question persists on the scalability of the QWFET and its ability to compete with Si MOSFETs at lower supply voltage for the 15 nm technology node and below.

Recently, higher indium concentration  $In_{0.7}Ga_{0.3}As$  and InAs channel QWFETs have been experimentally demonstrated with gate length ( $L_{\rm G}$ ) down to 50 nm with excellent short channel performance and high speed response operating at 0.5 V supply voltage [7–9], albeit with large separation between the source and drain metal electrodes ( $L_{\rm SD}$  = 2  $\mu$ m). In order to implement III–V QWFETs in future high-performance logic applications, its scalability both in terms of physical gate length as well as the overall footprint of the transistor should be thoroughly investigated.

In this paper, we provide a systematic study of the scalability of  $In_{0.7}Ga_{0.3}As$  QWFETs via two-dimensional numerical drift-diffusion (DD) simulation [10]. The paper is organized as follows. In Section 2, we perform calibration of the numerical simulator to the experimental 50 nm  $L_G$   $In_{0.7}Ga_{0.3}As$  QWFETs [7,8], to match both the ON-current in linear and saturation regime as well as the sub-threshold response. In Section 3, we investigate the effect of both lateral and vertical scaling on the  $In_{0.7}Ga_{0.3}As$  QWFET device

<sup>&</sup>lt;sup>a</sup> The Pennsylvania State University, University Park, PA 16802, USA

<sup>&</sup>lt;sup>b</sup> Virginia Tech, Blacksburg, VA 24061, USA

<sup>\*</sup> Corresponding author. Tel.: +1 814 865 0519; fax: +1 814 865 7065. E-mail address: euh125@psu.edu (E. Hwang).

performance down to physical gate length of 15 nm. In Section 4, we extract the effective carrier mobility in short-channel QWFETs and conclude that, with aggressive  $L_G$  scaling, the ballistic mobility limits the short channel mobility due to near ballistic transport in the channel, and conclude that the effective carrier injection velocity,  $v_{\rm eff}$ , near the source side is a quantitative and more pertinent indicator of transport in short-channel QWFETs than effective mobility. Finally, in Section 5, we provide a quantitative estimate of the degradation of short-channel performance of conventional  $In_{0.7}Ga_{0.3}As$  QWFETs with  $L_G = 15$  nm. Therefore, we introduce three different QWFET architectures in this section, provide a quantitative assessment of the logic figure of merit of three OWFETs, and propose the design for the ultimate scaled In<sub>0.7</sub>-Ga<sub>0.3</sub>As QWFET architecture suitable for 15 nm technology node and beyond logic applications. The proposed architecture is generic and could be applied to next generation antimonide-based QWFETs such as  $InAs_xSb_{1-x}$  and  $In_vGa_{1-v}Sb$ , currently under investigation [11].

#### 2. Device simulation

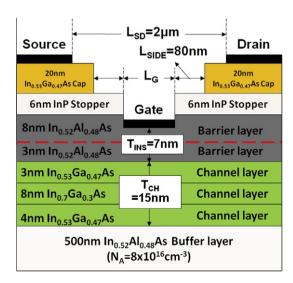

Fig. 1 presents the schematic of the simulated and experimental In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFET. The dimensions of the device are identical to those reported in [7]. The composite channel consists of 3/8/ 4 nm thick  $In_{0.53}Ga_{0.47}As/In_{0.7}Ga_{0.3}As/In_{0.53}Ga_{0.47}As$  and features both regular and buried-Pt gate stack with  $L_{\rm G}$  = 50 nm in direct contact with the upper In<sub>0.52</sub>Al<sub>0.48</sub>As barrier forming a Schottky junction. The In<sub>0.52</sub>Al<sub>0.48</sub>As barrier is doped with Si delta-doping of  $5.5 \times 10^{12} \, \text{cm}^{-2}$  which is placed 3 nm above the composite channel to provide electron carriers into the channel. The 20 nm thick In<sub>0.53</sub>Ga<sub>0.47</sub>As cap layer is n-type, heavily-doped one with  $1 \times 10^{19} \, \text{cm}^{-3}$ . The devices have total channel thickness of  $T_{CH}$  = 15 nm, the lateral spacer thickness (distance between the n + doped layer and the gate electrode) of  $L_{\text{SIDE}}$  = 80 nm and a source to drain electrode spacing of  $L_{\rm SD}$  = 2  $\mu m$ . While the regular Pt Schottky gate device has an effective insulator thickness of  $T_{\rm INS}$  = 11 nm, the buried-Pt gate device has  $T_{\rm INS}$  = 7 nm. By modelling the same device structure as the real device, we attempt to simulate the associated access resistance including the contact ones ( $R_{\text{CONTACT}} = 50 \Omega \mu \text{m}$ ).

**Fig. 1.** Schematic of  $In_{0.7}Ga_{0.3}As$  QWFET device structure. The insulator thickness  $(T_{INS})$ , the channel thickness  $(T_{CH})$ , the distance between source and drain  $(L_{SD})$ , and the distance between the gate and cap layer  $(L_{SIDE})$  are specified. While the regular Pt Schottky gate device has an effective insulator thickness of  $T_{INS}$  = 11 nm, the buried-Pt gate device has  $T_{INS}$  = 7 nm. For the calibration, the gate length  $(L_G)$  is equal to 50 nm.

The two dimensional numerical simulation self-consistently solves the Poisson's equation with carrier continuity equation using a drift-diffusion model. To accurately capture the non-equilibrium carrier transport (such as velocity overshoot effect), we employ the Canali mobility model (1) [12] with appropriate modifications.

$$\mu(E) = \frac{(\alpha + 1)\mu_{low}}{\alpha + \left[1 + \left(\frac{(\alpha + 1)\mu_{low}E}{\nu_{sat}}\right)^{\beta}\right]^{\frac{1}{\beta}}}$$

(1)

The model parameters are determined by matching the simulation results to the experimental results. The parameters used in the calibration exercise are  $\mu_{low}(ln_{0.7}Ga_{0.3}As)=12,000~cm^2/V~s,~\mu_{lo-w}(ln_{0.53}Ga_{0.47}As)=10,000~cm^2/V~s,~\nu_{sat}=9.5\times10^7~cm/s,~\alpha=0~$  and  $\beta=0.6$ . Here,  $\nu_{sat}$  is the saturation velocity and  $\beta$  is a constant reflecting the steepness of the carrier velocity profile in the channel. They are defined as  $\nu_{sat}=0.93\times10^7~cm/s$  and  $\beta=2$  for electrons by default. However, in order to take into account the velocity overshoot effect at high fields and maintain the accurate velocity at low fields, a high saturation velocity value and a lower than unity beta value are used within the drift–diffusion simulation framework, which is similar to the approach outlined by Bude [13]. Therefore, it leads to accomplish simulation time efficiency and accuracy simultaneously [14].

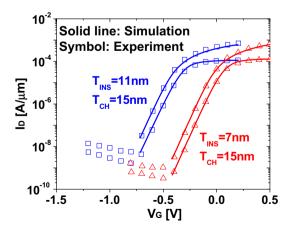

In order to calibrate the simulation results with the experimental results in [7], two 50 nm gate-length  $\rm In_{0.7}Ga_{0.3}As$  QWFET designs with regular and buried-Pt gate electrodes are simulated with  $T_{\rm INS}$  = 7 nm and  $T_{\rm INS}$  = 11 nm, respectively. Fig. 2 shows excellent agreement between the simulated and the experimental results in both sub-threshold as well as in upper-threshold regime, thereby validating the approximation of the carrier transport model and the model parameters defined in this paper. The gate leakage portion of the device transfer characteristics was not modelled in our simulation results, and will not affect the conclusions obtained in the succeeding sections.

#### 3. Effect of lateral and vertical scaling

In this section, we first assess the impact of physical gate length scaling on the performance of conventional  $In_{0.7}Ga_{0.3}As$  QWFETs for 15 nm logic applications and beyond. We simulate  $In_{0.7}Ga_{0.3}As$  QWFETs with buried-Pt gate ( $T_{INS} = 7$  nm,  $T_{CH} = 15$  nm) for different gate-lengths ranging from 15 to 200 nm and evaluate the various

**Fig. 2.** Transfer characteristics of 50 nm  $L_{\rm G}$  In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs featuring both the regular Pt Schottky gate and the buried-Pt gate. The simulation results are calibrated when  $T_{\rm INS}$  = 11 nm (blue, solid) and  $T_{\rm INS}$  = 7 nm (red, solid). (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

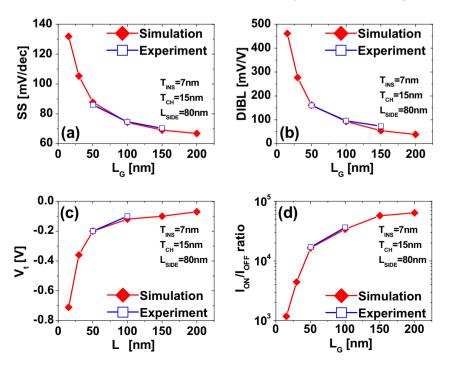

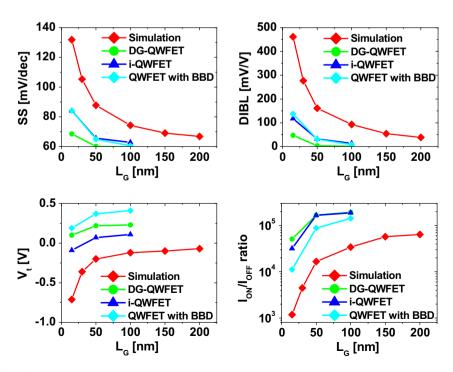

figures of merit such as sub-threshold slope (SS), drain-induced barrier lowering (DIBL), threshold voltage  $(V_t)$  roll-off, and  $I_{\rm ON}/I_{\rm OFF}$  ratio. The figures of merit are compared with the experimental results [7] as illustrated in Fig. 3. As a result of the  $L_{\rm G}$  scaling, it results in large DIBL, causing the degradation of SS. This is accompanied by significant  $V_{\rm t}$  roll-off trend and the consequent decrease in  $I_{\rm ON}/I_{\rm OFF}$  ratio. To extract the  $I_{\rm ON}$  and  $I_{\rm OFF}$ , we have applied the methodology outlined by Chau et al. [1]. First,  $V_{\rm t}$  is defined as a value of gate voltage where the drain current ( $I_{\rm D}$ ) corresponds to 1  $\mu$ A/ $\mu$ m. Then,  $I_{\rm ON}$  is determined from the value of  $I_{\rm D}$  at which  $V_{\rm GS}$  corresponds to approximately two-third of  $V_{\rm CC}$  above  $V_{\rm t}$ . In a similar manner,  $I_{\rm OFF}$  is chosen as  $I_{\rm D}$  where  $V_{\rm GS}$  is one-third of  $V_{\rm CC}$  below  $V_{\rm t}$ .

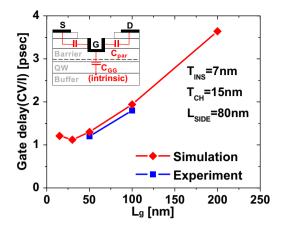

Intrinsic gate delay (CV/I), as shown in Fig. 4, is another important figure of merit for high-speed logic applications. In extracting the CV/I, C is the gate capacitance ( $C_{\rm GG}$ ) defined at the same gate bias condition as  $I_{\rm ON}$ , I is  $I_{\rm ON}$  and V is the supply voltage of operation. The gate capacitance takes into account the barrier capacitance as well as the quantum capacitance in the channel arising from the limited density of states (DOS) as well as the parasitic capacitance from the gate to source/drain fringing electric field. The total gate capacitance is reduced with reducing  $L_{\rm G}$  due to geometric effect, thereby, leading to the decrease in gate delay. However, at  $L_{\rm G}$  = 15 nm, the inherent parasitic capacitances arising from gate to source/drain fringing electric field form a significant portion of the total gate capacitance, and, therefore,  $C_{\rm GG}$  is hardly reduced further [15,16]. In addition,  $I_{\rm ON}$  is greatly decreased due to poor electrostatics, thus adversely affecting the total gate delay.

In addition to  $L_G$  scaling,  $L_{SIDE}$  needs to be scaled in order to achieve a small device footprint needed for 15 nm or below. Initially,  $L_{SIDE}$  is kept at 80 nm and subsequently decreased to 15 nm. Table 1 summarizes the loss in electrostatic integrity of the QWFET as a direct consequence of  $L_{SIDE}$  scaling at the 15 nm  $L_G$ . To sustain a scaling path for QWFET with 15 nm physical gate length, we first normalize the physical gate length to the electrostatic scaling length of the device. As Yan et al. indicate in [17], the scaling rule is dictated by both electrostatic scaling length ( $\lambda$ ) in (2) and aspect ratio ( $\gamma = L_G/\lambda$ ).

Fig. 4. Intrinsic gate delay (CV/I) versus  $L_G$  for  $In_{0.7}Ga_{0.3}As$  QWFETs.

$$\lambda = \sqrt{\frac{\varepsilon_{Si}}{\varepsilon_{ov}} t_{Si} t_{ox}} \tag{2}$$

Here, the electrostatic model originally developed for fully-depleted SOI MOSFETs (FD-MOSFETs) is applicable for conventional  $In_{0.7}Ga_{0.3}As$  QWFETs and  $\lambda$  is calculated to be 10 nm by taking the relative contribution of In<sub>0.52</sub>Al<sub>0.48</sub>As and composite channel InGaAs layer and their effective permittivity values into account [17,18]. To maintain the appropriate sub-threshold behaviour,  $\gamma$ should be maintained at least at 5 and higher. Therefore, one of the promising options is the vertical scaling of the conventional  $In_{0.7}Ga_{0.3}As$  OWFETs leading to reduction of both  $T_{INS}$  and  $T_{CH}$ . Table 1 summarizes the improvement in the device performance with the vertical scaling. The insulator thickness and the channel thickness are reduced from 7 to 4 nm and from 15 to 7 nm, respectively. The simulation results indicate that vertical scaling indeed contributes to a better electrostatic integrity and, thereby improves the SS, DIBL,  $V_t$ -roll off and  $I_{\rm ON}/I_{\rm OFF}$  ratio. To further improve the electrostatic integrity of the In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs, we also investigate the effect of compensation doping  $(N_A)$  of the bot-

**Fig. 3.** Logic figures of merit for  $In_{0.7}Ga_{0.3}As$  QWFETs with different  $L_G$ .  $In_{0.7}Ga_{0.3}As$  QWFETs with buried-Pt gate ( $T_{INS} = 7$  nm,  $T_{CH} = 15$  nm) for different gate-lengths ranging from 15 to 200 nm are designed and the logic figures of merit (SS, DIBL,  $V_{t_1}I_{ON}/I_{OFF}$  ratio) are extracted.

**Table 1**Device performance comparison. At  $L_G$  = 15 nm,  $L_{SIDE}$  is reduced from 80 nm to 15 nm (in column 2). To further improve the device performance,  $T_{INS}$  and  $T_{CH}$  are reduced from 7 nm to 4 nm and from 15 nm to 7 nm, respectively (in column 3). To increase the buffer layer doping ( $N_A$ ) to 1 × 10<sup>18</sup> cm<sup>-3</sup> leads to improvement in the electrostatic integrity, but the increase in access resistance suppresses the ON-current (in column 4). Bold values indicate the change in the current simulation from the previous simulation.

| $L_{\rm G} = 15 \text{ nm}$ ( $V_{\rm CC} = 0.5$ ) | $T_{\text{INS}} = 7 \text{ nm}$<br>$T_{\text{CH}} = 15 \text{ nm}$<br>$L_{\text{SIDE}} = 80 \text{ nm}$<br>$N_{\text{A}} = 8 \times 10^{16} \text{ cm}^{-3}$ | $T_{\rm INS}$ = 7 nm<br>$T_{\rm CH}$ = 15 nm<br>$L_{\rm SIDE}$ = 15 nm<br>$N_{\rm A}$ = 8 × 10 <sup>16</sup> cm <sup>-3</sup> | $T_{\text{INS}}$ = 4 nm<br>$T_{\text{CH}}$ = 7 nm<br>$L_{\text{SIDE}}$ = 15 nm<br>$N_{\text{A}}$ = 8 × 10 <sup>16</sup> cm <sup>-3</sup> | $T_{\rm INS} = 4 \text{ nm}$<br>$T_{\rm CH} = 7 \text{ nm}$<br>$L_{\rm SIDE} = 15 \text{ nm}$<br>$N_{\rm a} = 1 \times 10^{18} \text{ cm}^{-3}$ |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| DIBL (mV/V)                                        | 461.3                                                                                                                                                        | 595                                                                                                                           | 298                                                                                                                                      | 135.7                                                                                                                                           |

| SS (mV/dec)                                        | 131.9                                                                                                                                                        | 152.6                                                                                                                         | 109.9                                                                                                                                    | 101.8                                                                                                                                           |

| $V_{\rm t.sat}$ (V)                                | -0.71                                                                                                                                                        | -0.85                                                                                                                         | -0.24                                                                                                                                    | 0.26                                                                                                                                            |

| $I_{\rm ON}/I_{\rm OFF}$                           | $1.18 \times 10^{3}$                                                                                                                                         | $5.71 \times 10^{2}$                                                                                                          | $3.59 \times 10^{3}$                                                                                                                     | $4.67 \times 10^{3}$                                                                                                                            |

| $I_{ON} (A/\mu m)$                                 | $6.890 \times 10^{-5}$                                                                                                                                       | $4.963 \times 10^{-5}$                                                                                                        | $1.184 \times 10^{-4}$                                                                                                                   | $1.115 \times 10^{-4}$                                                                                                                          |

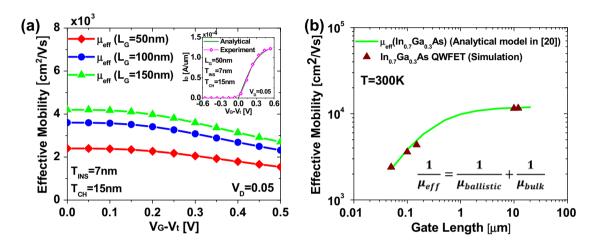

**Fig. 5.** (a) The effective mobility as a function of gate bias for  $\ln_{0.7}Ga_{0.3}As$  QWFETs with 50 nm, 100 nm and 150 nm  $L_G$ . (b) The effective mobility as a function of  $L_G$  for  $\ln_{0.7}Ga_{0.3}As$  QWFETs. The effective mobility values of QWFETs (brown, triangle) from simulations are in close agreement with the one obtained from Mathiessen's rule  $\left(1/\mu_{eff} = 1/\mu_{bullistic} + 1/\mu_{bull}\right)$  in [20] (green, solid). (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

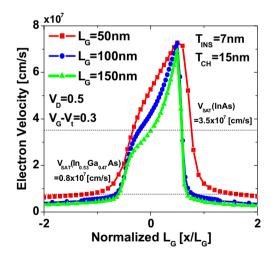

**Fig. 6.** The effective carrier injection velocity profile in the channel with the channel normalized.  $v_{\rm eff}$  for 50, 100 and 150 nm  $L_{\rm G}$  In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs is directly extracted from the simulation at the conduction band peak near the source end at  $V_{\rm D}$  = 0.5 V and  $V_{\rm G}-V_{\rm t}$  = 0.3 V.  $v_{\rm sat}$  for InAs and In<sub>0.53</sub>Ga<sub>0.47</sub>As are obtained from [23].

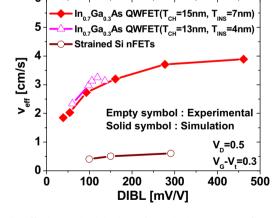

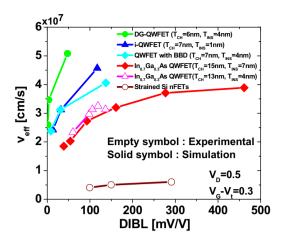

**Fig. 7.** The effective carrier injection velocity ( $v_{\rm eff}$ ) versus DIBL for various  $L_{\rm G}$   $\ln_{0.7} {\rm Ga}_{0.3} {\rm As}$  QWFETs from simulations (solid) with the experimental data for-  $\ln_{0.7} {\rm Ga}_{0.3} {\rm As}$  QWFET and strained Si nFETs (symbols) at  $V_{\rm D} = 0.5 \, {\rm V}$  and  $V_{\rm G} = V_{\rm t} = 0.3 \, {\rm V}$ .  $\ln_{0.7} {\rm Ga}_{0.3} {\rm As}$  QWFETs from simulations have  $T_{\rm INS} = 7 \, {\rm nm}$  and  $T_{\rm CH} = 15 \, {\rm nm}$ , while the experimental  $\ln_{0.7} {\rm Ga}_{0.3} {\rm As}$  QWFETs from [24,25] have  $T_{\rm INS} = 4 \, {\rm nm}$  and  $T_{\rm CH} = 13 \, {\rm nm}$ . Also,  $v_{\rm eff}$  for strained Si nFETs is plotted together at the same bias conditions.

tom barrier layer on the device performance. As  $N_{\rm A}$  is increased from  $8 \times 10^{16} \, {\rm cm^{-3}}$  to  $1 \times 10^{18} \, {\rm cm^{-3}}$ , both DIBL and SS improve and  $V_{\rm t}$  increases. However, increasing the buffer layer doping results in higher access resistance, as the increased p-type doping in the bottom barrier layer pinches off the access regions leading to high  $R_{\rm FXT}$ , which reduces the ON-current, as shown in Table 1.

#### 4. Ballistic effect and short channel transport

As the device dimension is scaled down, there is a transition in device transport behavior from the diffusive toward the ballistic limit. Unlike silicon MOSFETs with moderate mobility values,

QWFETs with III–V compound semiconductors possess high electron mobility up to  $15,000~\text{cm}^2/\text{V}$  s or even higher. For example,  $\text{In}_{0.7}\text{Ga}_{0.3}\text{As}$  QWFET has a low-field electron mobility of  $12,000~\text{cm}^2/\text{V}$  s with carrier density of  $2\times10^{12}~\text{cm}^{-2}$  in the channel and thus, its mean-free-path is calculated to be approximately 150 nm. Therefore, QWFETs with gate-length approaching 15 nm are expected to operate close to the ballistic limit [19] across a range of operating bias conditions. In order to quantify the significance of ballistic transport, we have investigated the short-channel mobility of QWFETs in detail in this section.

As mentioned earlier, the high carrier mobility in long channel III–V based QWFET arises from a combination of its low electron mass, reduced Columbic scattering and lower interface roughness scattering. However, in the short-channel QWFETs, electrons are launched with thermal velocity ( $V_{\rm th}$ ) from source into the channel and traverse the channel encountering few collisions. In such a scenario, the actual channel resistance is weakly dependent on the

physical gate length of the device, and any attempt to estimate the short-channel mobility as a function of  $L_{\rm G}$  results in values lower than their long channel values. In this respect, the effective carrier mobility for short-channel devices operating close to the ballistic limit is primarily limited by the so-called "ballistic mobility", whereas the one for long-channel devices is primarily governed by the bulk mobility. The ballistic mobility is given by Eq. (3) in [20].

$$\mu_{ballistic} = \frac{2qL}{\pi m V_{\rm rb}} \tag{3}$$

In order to extract the effective mobility for short-channel  $In_{0.7}$ - $Ga_{0.3}$ As QWFETs, the experimental transfer characteristics of  $In_{0.7}$ - $Ga_{0.3}$ As QWFETs (50 nm, 100 nm and 150 nm  $L_{\rm G}$ ) are obtained [7.8].

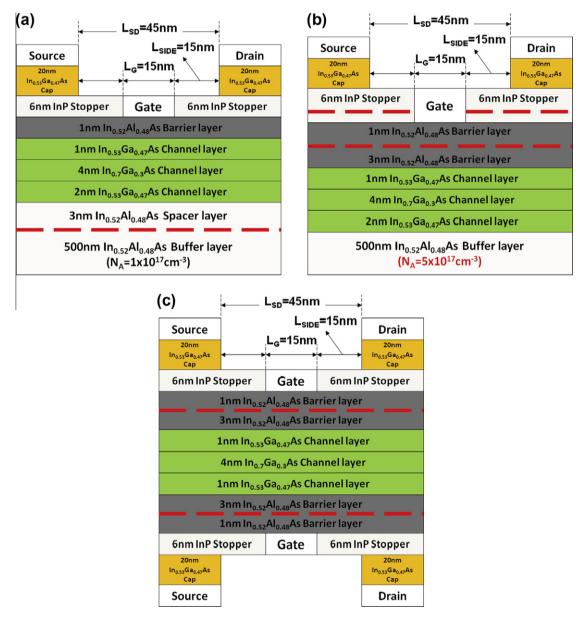

**Fig. 8.** (a) Schematic of 15 nm  $L_G$  inverted- $In_{0.7}Ga_{0.3}As$  QWFET with  $T_{INS}$  = 1 nm and  $T_{CH}$  = 7 nm. (b) Schematic of 15 nm  $L_G$   $In_{0.7}Ga_{0.3}As$  QWFET with high bottom-barrier doping ( $N_A$  = 5 × 10<sup>17</sup> cm<sup>-3</sup>),  $T_{INS}$  = 4 nm and  $T_{CH}$  = 7 nm. To mitigate the higher access resistance problem, the second delta doping layer is incorporated 1 nm above  $In_{0.52}AI_{0.48}As$  barrier layer in the InP etch stopper layer. (c) Schematic of 15 nm  $L_G$  double-gate  $In_{0.7}Ga_{0.3}As$  QWFET with  $T_{INS}$  = 4 nm and  $T_{CH}$  = 6 nm. To make suitable for 60 nm gate-pitch footprint,  $L_{SIDE}$  is aggressively reduced down to 15 nm.

$$I_{\rm D} = C_{\rm GG} \frac{w}{L_{\rm eff}} (V_{\rm G} - V_{\rm t}) \frac{\mu_{\rm low}}{(1 + (\theta(V_{\rm G} - V_{\rm t}))^{\beta})^{\frac{1}{\beta}}} V_{\rm D} \tag{4}$$

Effective electron mobility values in the linear operation regime are calculated using Eq. (4) in [21], where  $C_{\rm GG}$  is a combination of the barrier capacitance and the centroid capacitance. Also, both  $\theta$  and  $\beta$  are adjustable parameters to reflect the dependence of the gate electric field on the channel transport. As seen in the inset of Fig. 5 ( $L_{\rm G}$  = 50 nm), the deviation of the transfer characteristic from linear Vg dependence at high gate bias regime is captured by introducing  $\theta$  = 2.8 and  $\beta$  = 3 (analytical model with  $\beta$  = 1 and higher values of  $\theta$  results in the underestimation of  $I_{\rm D}$ ). The adjusted  $\theta$  and  $\beta$  match well with the experiments for 50 nm, 100 nm and 150 nm  $L_{\rm G}$  In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs. Physically, the higher value of  $\beta$  used in the analytical mobility model reflects the non-stationary effect related to the velocity overshoot near the drain end.

Fig. 5a shows the effective mobility as a function of gate bias for  $\ln_{0.7}Ga_{0.3}As$  QWFETs with 50 nm, 100 nm and 150 nm gate-length. It is clear that the effective mobility reduces as  $L_{\rm G}$  is scaled down. In Fig. 5b, the effective channel mobility of short-channel QWFETs is in close agreement with the one obtained from Mathiessen's rule  $(1/\mu_{\rm eff}=1/\mu_{ballistic}+1/\mu_{bulk})$  in [20] which directly arises from the transmission factor being the ratio of the mean-free-path to the physical  $L_{\rm G}$ . However, this apparent degradation in short channel mobility is not an actual concern for scaled  $\ln_{0.7}Ga_{0.3}As$  QWFET performance. Rather, the effective carrier injection velocity ( $v_{\rm eff}$ ) at the conduction band peak near the source end (injection velocity) becomes more significant. The ON-current is primarily limited, not by the effective carrier mobility, but by the effective carrier injection velocity as short-channel devices enter the ballistic regime [221].

$$I_{\rm D} = C_{\rm OX} W v_{\rm T} \left(\frac{t_{\rm c}}{1+r_{\rm c}}\right) (V_{\rm GS} - V_{\rm t}) \tag{5}$$

$$v_{inj} = v_T \left( \frac{t_C}{1 + r_C} \right) \tag{6}$$

Eq. (5) shows the dependence of drain current on the transmission  $(t_c = \lambda/(L + \lambda))$  and reflection coefficients  $(r_c = L/(L + \lambda))$  as predicted from scattering theory [22] and Eq. (6) shows the dependence of injection velocity on the transmission coefficient. Consequently, due to the low electron mass in  $In_{0.7}Ga_{0.3}As$  QWFET and very little back scattering from the channel into the source, a high injection velocity can be achieved. Further, the increase in the effective injection velocity with  $L_G$  scaling improves the drive current.

From a careful calibration of the saturation ON-current for 50 nm, 100 nm and 150 nm In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs [8] by adjusting  $v_{\rm sat}$  and  $\beta$  [12], the effective electron velocity is directly extracted from the plot of carrier velocity profile in Fig. 6 at the conduction band peak near the source end at  $V_D = 0.5 \text{ V}$  and  $V_G - V_t = 0.3 \text{ V}$ . InAs and  $In_{0.53}Ga_{0.47}As \ v_{sat}$  values are obtained from [23]. Fig. 7 plots  $v_{\rm eff}$  versus DIBL for  ${\rm In_{0.7}Ga_{0.3}As}$  QWFETs from 15 to 200 nm L<sub>G</sub>. Since the effective carrier injection velocity for In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs in [7] is not available, it is extracted from experimental data in [24] and compared with the simulation results. The In<sub>0.7-</sub>  $Ga_{0.3}As$  QWFETs in [24,25] possess  $T_{CH}$  = 13 nm,  $T_{INS}$  = 4 nm and  $L_{SI}$ DE = 80 nm with the gate-length ranging from 30 to 130 nm. Their effective carrier injection velocity values were also extracted under the same bias conditions. In Fig. 7, it is clearly shown that the effective carrier injection velocity increases as the electrostatic integrity aggravates. However, at a fixed DIBL value (100 mV/V), the simulation result shows about 6.9 times higher  $v_{\rm eff}$  for  ${\rm In_{0.7}Ga_{0.3}As}$ QWFETs than the one for strained Si nMOSFETs in [5] which is about  $4.06 \times 10^6$  cm/s at  $V_D = 0.5$  V and  $V_G - V_t = 0.3$  V. This increase in injection velocity for III-V compound semiconductors is a necessity in order to compensate for lower carrier density in the channel of III-V QWFETs due to the reduced density of states in In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs compared to Si MOSFETs.

**Fig. 9.** Logic figures of merit for different  $In_{0.7}Ga_{0.3}As$  QWFET device architectures. Compared to conventional  $In_{0.7}Ga_{0.3}As$  QWFETs (red line), the scalability of all three QWFETs is improved due to better device architecture schemes. Among them, double-gate  $In_{0.7}Ga_{0.3}As$  QWFET shows the best scalability and electrostatic integrity. (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

**Fig. 10.** The effective carrier injection velocity ( $v_{\rm eff}$ ) versus DIBL for different  $\ln_{0.7} Ga_{0.3}$ As QWFET device architectures. It indicates that the extracted  $v_{\rm eff}$  values for three QWFET architectures exceed that of the conventional QWFETs (red line). Consequently, amongst them, double-gate  $\ln_{0.7} Ga_{0.3}$ As QWFETs represent the highest  $v_{\rm eff}$  at a fixed DIBL value. (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

#### 5. Scalable QWFET architectures

Using the calibrated numerical simulation from Sections 3 and 4, three different  $In_{0.7}Ga_{0.3}As$  QWFET device architectures are studied; inverted QWFET (i-QWFET), QWFET with higher bottom-barrier doping (QWFET with BBD) and double-gate QWFET (DG-QWFET). For 15 nm node and beyond logic applications,  $L_{\rm G}$  and  $L_{\rm SIDE}$  are aggressively scaled down to 15 nm, thus making them suitable for a 60 nm contacted gate-pitch.

In an inverted- $In_{0.7}Ga_{0.3}As$  QWFET design shown in Fig. 8a,  $T_{CH}$ is kept at 7 nm and  $T_{INS}$  is reduced down to 1 nm, thereby, resulting in a better gate control. The gate leakage is ignored in this study since in future devices a high-k dielectric will be integrated with the QWFET architecture [26]. Next, we have investigated the  $In_{0.7}$ Ga<sub>0.3</sub>As QWFETs with higher bottom-barrier doping shown in Fig. 8b, where the overall electrostatic integrity is significantly improved compared to the conventional In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs. This QWFET with higher bottom-barrier doping has  $T_{INS} = 4 \text{ nm}$  and  $T_{\rm CH}$  = 7 nm. Additionally, to mitigate the high access resistance associated with the carrier depletion effects arising from higher bottom barrier p-type doping, a second delta doping layer is incorporated 1 nm above the In<sub>0.52</sub>Al<sub>0.48</sub>As barrier layer in the InP etch stopper layer. Finally, a double-gate In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFET structure is shown in Fig. 8c with  $T_{\rm INS}$  = 4 nm and  $T_{\rm CH}$  = 6 nm. Fig. 9 compares the logic figures of merit for the three different QWFET architectures. Compared to conventional In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs (red line), the scalability of all three QWFETs is improved due to better device architecture schemes. The effective carrier injection velocity versus DIBL is also plotted for three QWFET device architectures in Fig. 10. It indicates that the extracted  $v_{\rm eff}$  values for three QWFET architectures exceed that of the conventional QWFETs (red line). However, the reason for the different peak values of  $v_{\rm eff}$  at  $L_{\rm G}$  = 15 nm originates from the relationship between the mean-free-path  $(\lambda)$  and the effective mobility ( $\mu_{\rm eff}$ ) [19]. From  $D_n = V_{\rm th} \lambda/2$  and Einstein relation, the mean-free-path is dependent on the mobility values for the three different QWFET architectures which are different due to the gate-field dependence as captured quantitatively by the Canali transport model. Consequently, double-gate In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs exhibit the highest effective carrier injection velocity at a fixed DIBL value and deliver the best logic performance (SS, DIBL,  $V_{\rm t}$ -roll off and  $I_{\rm ON}/I_{\rm OFF}$  ratio) due to its electrostatic robustness, thus making it a strong candidate for the design of the ultimate scaled transistor.

#### 6. Conclusions

The scalability of conventional In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFETs is thoroughly investigated using a calibrated two-dimensional numerical drift-diffusion simulation. The non-equilibrium transport effect due to velocity overshoot in short channel In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFET is accurately captured in the modified drift-diffusion model. The conventional In<sub>0.7</sub>Ga<sub>0.3</sub>As QWEFTs show a poor scaling behaviour down to  $L_G$  = 15 nm. In addition to  $L_G$  scaling,  $L_{SIDE}$  is also scaled down to achieve a small device footprint, which degrades the overall device performance further and highlights the necessity of aggressive vertical scaling of the device. The importance of ballistic effect in short-channel QWFETs is emphasized and the limitations on the extracted effective short channel mobility due to ballistic effect are examined in detail. The significance of source side injection velocity is also pointed out for III-V QWFETs, thus making  $v_{\rm eff}$  versus DIBL an important figure of merit to benchmark various QWFET device architectures operating in the quasi or near ballistic regime. Finally, three alternate QWFET device architectures are proposed and thoroughly investigated for the 15 nm node and beyond logic applications. Amongst them, double-gate In<sub>0.7</sub>Ga<sub>0.3</sub>As QWFET has the best logic figures of merit and the highest effective carrier injection velocity, thus making it an ideal candidate for the design and demonstration of the ultimate scaled transistor.

#### References

- [1] Chau R, Datta S, Doczy M, Doyle B, Jin B, Kavalieros J, et al. Benchmarking nanotechnology for high-performance and low-power logic transistor applications. IEEE Trans Nanotechnol 2005;4(2):153–8.

- [2] Datta S, Ashley T, Brask J, Buckle L, Doczy M, Emeny M, et al. 85 nm gate length enhancement and depletion mode InSb quantum well transistors for ultra high speed and very low power digital logic applications. IEDM Tech Dig 2005:763–6.

- [3] Datta S, Dewey G, Fastenau JM, Hudait MK, Loubychev D, Liu WK, et al. Ultrahigh-speed 0.5 V supply voltage In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum-well transistors on silicon substrate. IEEE Electron Dev Lett 2007;28(8):685–7.

- [4] Kim DH, Alamo JA. 30 nm E-mode InAs PHEMTs for THz and Future Logic Applications. Int Electron Dev Meet (IEDM) 2008:719–22.

- [5] Dewey G, Hudait MK, Lee K, Pillarisetty R, Rachmady W, Radosavljevic M, et al. Carrier transport in high-mobility III-V quantum-well transistors and performance impact for high-speed low-power logic applications. IEEE Electron Dev Lett 2008;29(10):1094-7.

- [6] Dewey G, Kotlyar R, Pillarisetty R, Radosavljevic M, Rakshit T, Then H, Chau R. Logic performance evaluation and transport physics of schottky-gate III-V compound semiconductor quantum well field effect transistors for power supply voltages (VCC) ranging from 0.5 V to 1.0 V. Int Electron Dev Meet (IDEM) 2009:1–4.

- [7] Kim DH, Alamo JA, Lee JH, Seo KS. Logic suitability of 50-nm In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs for beyond-CMOS applications. IEEE Trans Electron Dev 2007;54(10): 2606–13.

- [8] Kim DH, Alamo JA, Lee JH, Seo KS. Performance evaluation of 50 nm  $\ln_{0.7}$ Ga $_{0.3}$ As HEMTs for beyond-CMOS logic applications. IEDM Tech Dig 2005:767–770.

- [9] Kim DH, Alamo JA, Lee JH, Seo KS. Beyond-CMOS: Impact of Side-Recess Spacing on the Logic Performance of 50 nm In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs. J Semicond Technol Sci 2006;6(3):146–53.

- [10] TCAD Sentaurus. Synopsys, Inc., Z-2007.03 edition; 2007.

- [11] Ali A, Madan H, Misra R, Hwang E, Agrawal A, Schiffer P, et al. Advanced composite high-k gate stack for mixed anion arsenide-antimonide quantum well transistors. Int Electron Dev Meet (IEDM) 2010;12:23–5.

- [12] Canali C, Majni G, Minder R, Ottaviani G. Electron and hole drift velocity measurements in silicon and their empirical relation to electric field and temperature. IEEE Trans Electron Dev 1975;22(11):1045–7.

- [13] Bude JD. MOSFET modeling into the ballistic regime. In: Proceedings SISPAD 2000; 23–6.

- [14] Granzner R, Polyakov VM, Schwierz F, Kittler M, Luyken RJ, Riosner W, et al. Simulation of nanoscale MOSFETs using modified drift-diffusion and hydrodynamic models and comparison with Monte Carlo results. Microelectron Eng 2006;83(2):241–6.

- [15] Khakifirooz A, Antoniadis DA. MOSFET performance scaling part I: historical trends. IEEE Trans Electron Dev 2008;55(6):1391–400.

- [16] Khakifirooz A, Antoniadis DA. MOSFET performance scaling-Part II: future directions. IEEE Trans Electron Dev 2008;55(6):1401–8.

- [17] Yan RH, Ourmazd A, Lee KF. Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans Electron Dev 1992;39(7):1704–10.

- [18] Kim DH, Alamo JA. Lateral and vertical scaling of In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs for Post-Si-CMOS logic applications. IEEE Trans Electron Dev 2008;55(10):2546–53.

- [19] Wang J, Lundstrom M. Ballistic transport in high electron mobility transistors. IEEE Trans Electron Dev 2003;50(7):1604–9.

- [20] Shur MS. Low ballistic mobility in submicron HEMTs. IEEE Electron Dev Lett 2002;23(9):511–3.

- [21] Huet K, Saint-Martin J, Bournel A, Galdin-Retailleau S, Dollfus P, Ghibaudo G, Mouis M. Monte Carlo study of apparent mobility reduction in nano-MOSFETs. In: Proceedings ESSDERC; 2007. p. 382–5.

- [22] Lundstrom M. Elementary scattering theory of the Si MOSFET. IEEE Electron Dev Lett 1997;18(7):361–3.

- [23] Cooke M. Digital III Vs review. III Vs Rev 2006;19:18–22.

- [24] Kim DH, Alamo JA, Antoniadis DA, Brar B. Extraction of virtual-source injection velocity in sub-100 nm III–V HFETs. Int Electron Dev Meet (IEDM) 2009:861–4.

- [25] Kim DH, Alamo JA. Scalability of sub-100 nm thin-channel InAs PHEMTs. In: International conference on indium phosphide and related materials; 2009. p. 132–5

- [26] Radosavljevic M, Chu-Kung B, Corcoran S, Dewey G, Hudait MK, Fastenau JM, Kavalieros J, Liu WK, Lubyshev D, Metz M, Millard K, Mukherjee N, Rachmady W, Shah U, Chau R. Advanced high-K gate dielectric for high-performance short-channel In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well field effect transistors on silicon substrate for low power logic applications. Int Electron Dev Meet (IEDM) 2009:319–22.